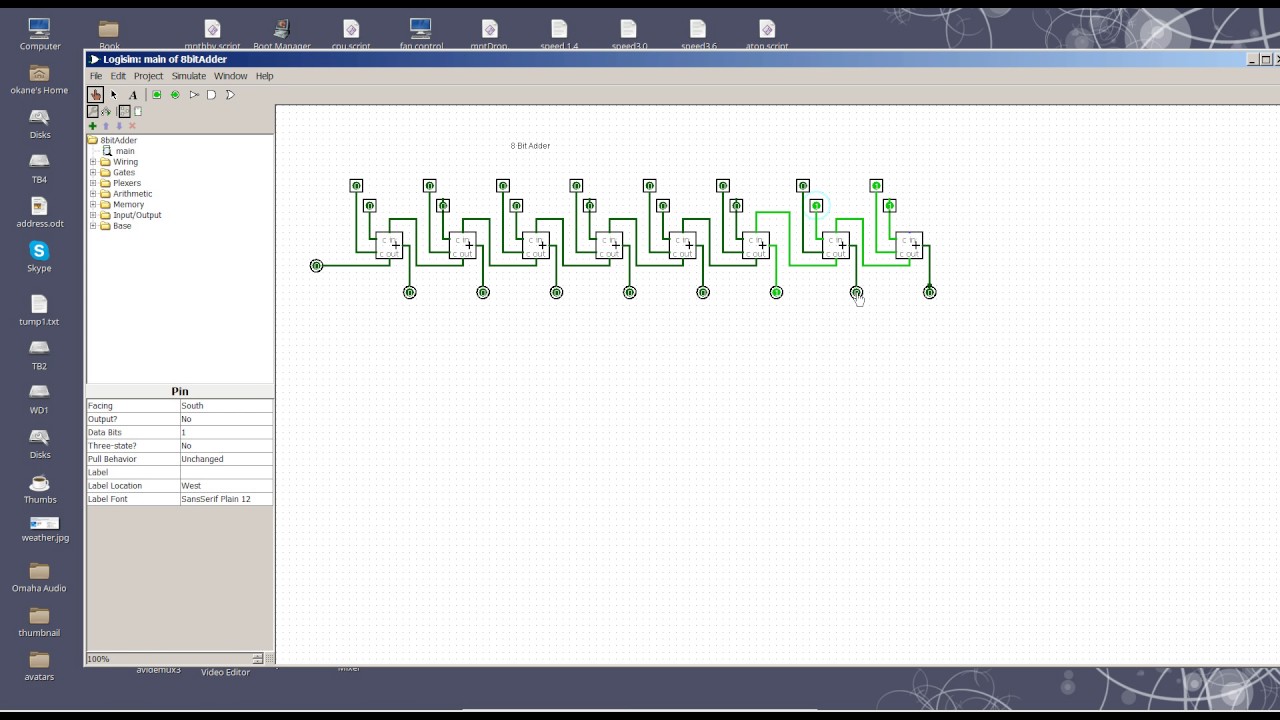

4.1.4 is designed to add or subtract 8−bit binary numbers using twos complement notation. The 8-bit adder/subtractor illustrated in Fig. (Here + signifies addition rather than OR)Īlternatively, if addition of A and B is required, then the control input is at logic 0 and number B is fed to the adder without complementing. The logic 1 on the control input is therefore also fed to the first carry input of the adder to be included in the addition, which for subtraction is therefore: with its value represented by the lower 7 bits (bit 0 to bit 6) and the sign represented by the most significant bit (bit 7). The result of this will be an 8-bit number in twos complement format, i.e. Twos complement subtraction in an 8-bit adder/subtractor requires that the 8-bit number at input B is complemented (inverted) and has 1 added to it, before being added to the 8-bit number at input A. When subtraction is required, the control input is set to logic 1, which causes the bit at any particular B input to be complemented by an XOR gate before being fed to input B of the full adder circuit. 4.1.3 but subtracts using the twos complement method described in Digital Electronics Module 1.5 (Ones and Twos Complement). This circuit adds in the same way as the adder in Fig. This is an 8-bit parallel adder/subtractor.

A further development of the parallel adder is shown in Fig.4.1.4. To carry out arithmetic however, it is also necessary to be able to subtract. 4.1.4 8−Bit Twos Complement Adder/Subtractor.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed